## 11-bit 10-MS/s SAR ADC with Capacitor Calibration for CDAC

## Ho-Yong Jung, Eunji Youn and Young-Chan Jang

Department of Electronic Engineering, Kumoh National Institute of Technology, Gumi, Korea

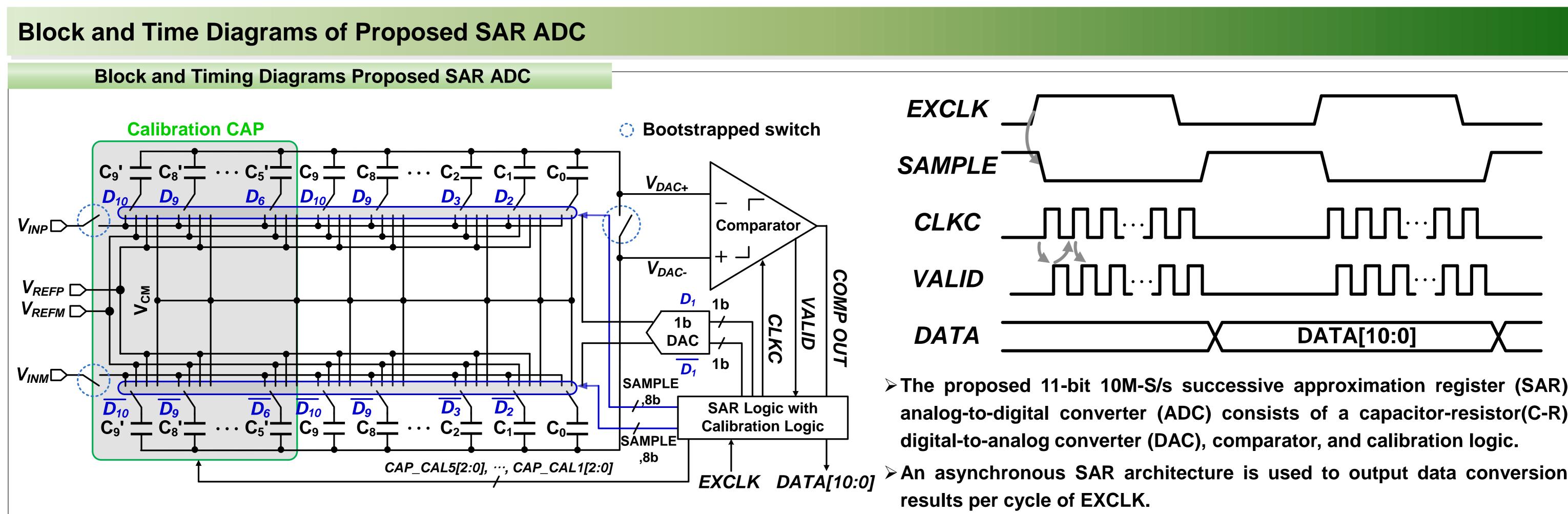

> The proposed 11-bit 10M-S/s successive approximation register (SAR) analog-to-digital converter (ADC) consists of a capacitor-resistor(C-R)

>An asynchronous SAR architecture is used to output data conversion

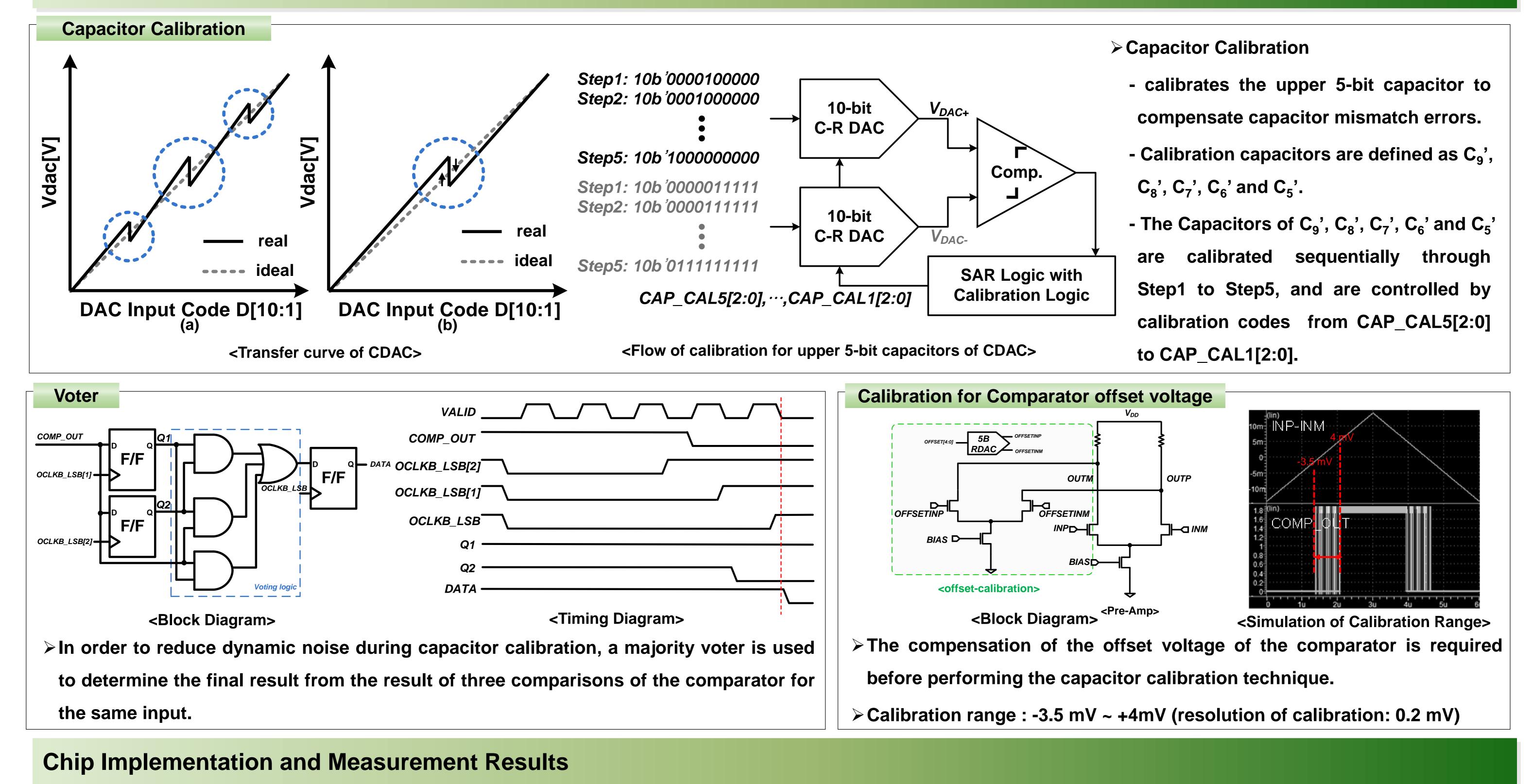

## **Proposed Capacitor Calibration and Building Block**

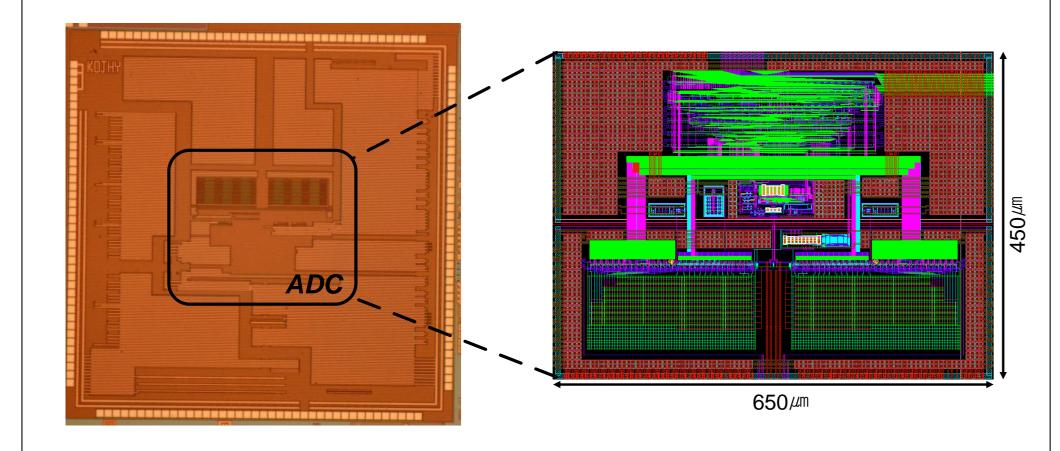

## **Chip Implementation**

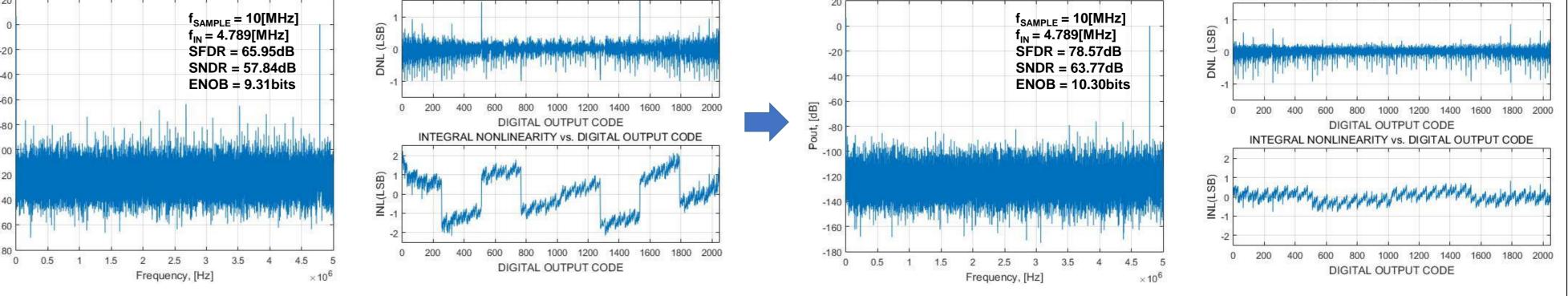

**Measurement Results**

DIFFERENTIAL NONLINEARITY vs. DIGITAL OUTPUT CODE

DIFFERENTIAL NONLINEARITY vs. DIGITAL OUTPUT CODE

<w/o capacitor calibration>

<w/ capacitor>

Proposed capacitor calibration used in the SAR ADC

- improves ENOB from 9.31 bits to 10.30 bits.

- improves DNL from -1/1.588 LSB to -0.975/0.855 LSB.

- improves INL from -2.171/2.227 LSB to -0.798/0.832 LSB.

Process & Supply: 180-nm 1-poly 5-metal CMOS process w/ MIM capacitor and 1.8V supply voltage  $\succ$  Power consumption: 583  $\mu$  $\succ$  Core area: 650  $\mu$ m  $\times$  450  $\mu$ m

**※** This research was conducted using the MPW program and CAD tools supported by IC Design Education Center (IDEC).